独立系のソフトウェアハウスが、高位合成を用いてFPGA開発を成功させた、先駆的なケース

HPC(high-performance computing)の推進と、画像処理の高速化に取り組んできたISPは、LSI設計現場などで普及が進む「高位合成」を利用し、自社ソフトウェア製品のアルゴリズムをハードウェア化する社内プロジェクトに着手。約3か月にわたった開発の過程で、最新のFPGA関連技術を蓄積しました。

今後、自社製品の高速化を目的としたFPGA化や、お客様へのソリューションのひとつとして、今回の開発ノウハウを多面的に展開していく考えです。

by wazalabo-editor 2015/01/6

プロジェクトの背景・ねらい

自社製品の高速化を目的としたFPGA化と同時に、放送現場のシビアな要求に応えるためにも、開発に着手

独立系ソフトハウスのシステム計画研究所(以下:ISP)では、HPC推進を目的に、さまざまなデジタル機器への搭載が進むFPGA(*2)の可能性に早くから着目し、その応用技術の開発と事業化を構想していました。2013年初頭、このFPGAを包含したハードウェアの開発環境を社内に整備。まず、ISPの自社ブランド商品として展開している高品質クロマキー合成ソフトウェア「ROBUSKEY(ロバスキー)」をハードウェア化するためのプロジェクトを、2014年8月に発足させています。

「ROBUSKEYは、弊社の所有するクロマキーアルゴリズムの名称で、従来はソフトウェアベースで提供されてきました。設備の不具合などが原因の放送事故が許されない放送業界からは、PCよりも信頼性・可用性が高く、特定の用途に最適化した機器が求められていました。ROBUSKEYのハードウェア化に取り組むきっかけのひとつには、こうした背景もあったのです」。山本真司は、本プロジェクトのもうひとつのねらいを、このように説明します。

(*2)FPGA:Field Programmable Gate Array。論理LSIの一種。設計者のねらいに沿った回路構成を短期間で実現でき、しかも、何度でも回路の書き換えが可能。

ハードウェア開発のプロセスと、適用技術

開発生産性の向上を図るため、「高位合成」を用いてFPGA開発を推進

ISPではROBUSKEYのハードウェア化に際して、FPGAの開発を社外に委託することはせず、自社のソフトウェア技術者が中心となって取り組むことにしました。開発を阻む壁になったのは、FPGAにプログラミングする回路規模の大きさでした。ROBUSKEYのコアのコードは比較的小規模だというのが、当初の認識でした。ところが、いざハードウェア化を開始してみると、この複雑なアルゴリズムを処理するには、膨大な規模の回路が必要だとわかったのです。

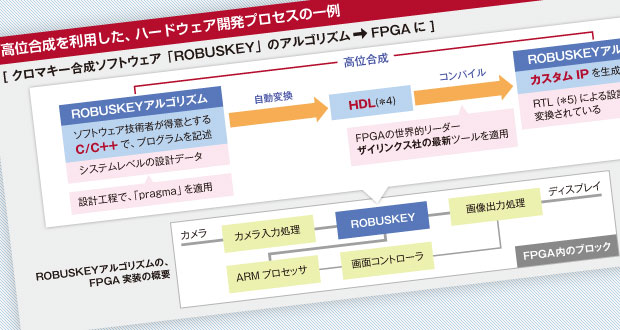

そこでISPでは、近年のLSI設計現場で実用的な技術として確立されてきた「高位合成(*3)」を利用し、開発生産性の向上を図りました。ISP社内で行った実際の開発プロセスと適用技術を、下図で説明します。

図のようなプロセスを経て、ROBUSKEYアルゴリズムのハードウェア化が実現できたポイントは、2つあります。

ひとつは、HDL(*4)での記述部分を少なくし、ほぼC言語だけを用いてハードウェア開発を進めたことです。ISPの技術者にとっては使い慣れた言語であり、シミュレーションによるトライ&エラーがしやすかったというメリットも得ています。そのうえで、前述した「高位合成」を利用し、開発効率の向上を図ったことが、大きなポイントでした。

ふたつめの成功要因は、HDLおよび RTL(*5)の設計データを正確に評価できる“目利き”役が、社内に存在したことです。「FPGAの開発にあたっては、HDLとRTLが、回路図として問題ないレベルのデータになっているかどうかを判断する必要があります」(大和田浩司)。この部分を担ったのが、FPGAの開発スキルを保有する、ハードウェア技術者の大和田でした。「HDLをコンパイルするためのツールが近年、急激に進化したことも、成功の要因だと考えます。今回のプロジェクトでは、FPGAの世界的リーダーであるザイリンクス社の最新ツールを適用しており、処理スピードの低下を招くことなく、開発生産性を飛躍的に向上することができました」(大和田)。

高位合成を利用した今回の開発は、単一のプロジェクトではなく、ISPにおけるHPC推進と、画像データ処理の高速化を目的とした最新技術・ノウハウを広範囲に展開することを、念頭に置いた取り組みでした。「今後、他のプロジェクトへの適用などを考慮すれば、よりクォリティの高いハードウェア開発のノウハウを蓄積しておく必要があります。例えば高位合成の際に、C言語では詳細に表現/指定できない動作を指示するためのpragma(*7)の使い方などです」と、満田賢一郎は話します。

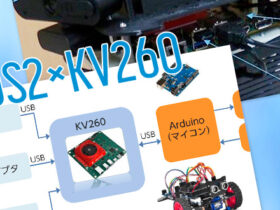

加えて、今後のFPGA開発のトレンドを見据えて、一般的なFPGAではなく、ARMを搭載したSOC(*6)である「Zynq」をハードウェアボードに採用。特定の用途に絞った専用の回路を内部に搭載することで高速化が実現できるこの「Zynq」に、ROBUSKEYのアルゴリズムを移植する開発案件として、このプロジェクトを推進しました。

(*4) HDL:集積回路の設計などを行なう際に用いられるコンピュータ言語。プログラミング言語に似た構文や表記法を持ち、回路に含まれる素子の構成や動作条件、素子間の配線などを記述できる。

(*5) RTL(Register Transfer Level):論理回路を、ハードウェア記述言語で記述する際の手法。

(*6) SOC(システム・オン・チップ):ひとつの半導体の中に、一般的なCPUである「ARM」と、「FPGA」が両方搭載されている半導体製品。

(*7) pragma (プラグマ):コンパイラに特定の情報を渡すための方法。コンパイルの内容を、詳細にわたって制御できる。

予想される導入成果

手軽に持ち歩ける『ポケットROBUSKEY』や、スイッチャーに組み込める製品も可能に

本プロジェクトを牽引した山本は、「独立系のソフトウェアハウスが、高位合成を用いてFPGA開発を成功させたケースが明示的に発表されたという例は、目にしたことがありません。しかもこの回路規模での開発では、先行事例ではないかと思っています」と話します。

ROBUSKEYアルゴリズムのハードウェア化が実現したことで、「たとえば、手軽に持ち歩ける『ポケットROBUSKEY』というユニークなコンセプトの製品化が可能になります」と、大和田は言います。PCという“呪縛”から解放されることで、放送現場で使用されているスイッチャーに組み込めるタイプの製品も、実現可能になります。

今後の展望・構想

ソフトウェア製品群のIP化を目指す

ISPでは今回のFPGA開発実績を踏まえて、ROBUSKEY以外にもラインナップしている美肌ライブラリなどの画像処理製品のアルゴリズムを順次、ハードウェア化していく計画を持っています。

一方、山本は「われわれが目指す究極の進化の形態は、当社ソフトウェア製品群のIP化です」と明かします。つまり、FPGAの回路をバイナリの形で、ハードウェアメーカーに提供することを構想しています。ISPは今後も、社内で活躍するソフトウェア技術者とハードウェア技術者の長所を融合して最善の開発成果を導き出し、HPC領域における革新的な商品/ソリューションをリリースしていく考えです。